|

计数器原理

计数器是数字系统中用的较多的基本逻辑器件,它的基本功能是统计时钟脉冲的个数,即实现计数操作,它也可用与分频、定时、产生节拍脉冲和脉冲序列等。例如,计算机中的时序发生器、分频器、指令计数器等都要使用计数器。

计数器的种类很多。按构成计数器中的各触发器是否使用一个时钟脉冲源来分,可分为同步计数器和异步计数器;按进位体制的不同,可分为二进制计数器、十进制计数器和任意进制计数器;按计数过程中数字增减趋势的不同,可分为加法计数器、减法计数器和可逆计数器;还有可预制数和可编计数器等等。

1、 用D触发器构成异步二进制加法/减法计数器

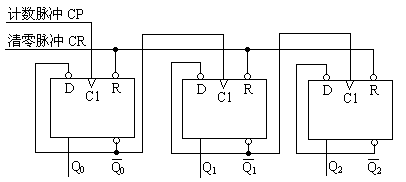

图1 3位二进制异步加法器

如上图1所示,是由3个上升沿触发的D触发器组成的3位二进制异步加法器。图中各个触发器的反相输出端与该触发器的D输入端相连,就把D触发器转换成为计数型触发器T。

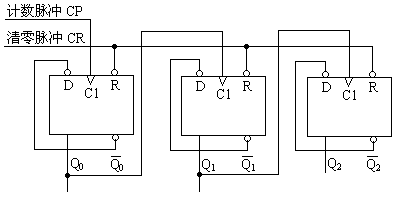

将上图加以少许改变后,即将低位触发器的Q端与高一位的CP端相连,就得到3位二进制异步减法器,如下所示:

图2 3位二进制异步减法器

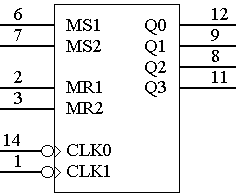

2、异步集成计数器74LS90

74LS90为中规模TTL集成计数器,可实现二分频、五分频和十分频等功能,它由一个二进制计数器和一个五进制计数器构成。其引脚排列图和功能表如下所示:

图3 74LS90的引脚排列图

表1 74LS90的功能表

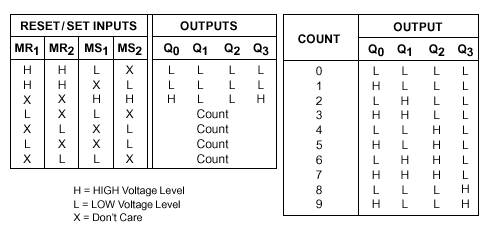

3、中规模十进制计数器74LS192(或CC40192)

74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:

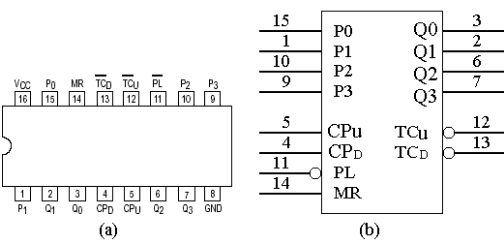

图4 74LS192的引脚排列及逻辑符号

(a)引脚排列 (b) 逻辑符号

图中:PL为置数端,CPU为加计数端,CPD为减计数端,TCU为非同步进位输出端, TCD为非同步借位输出端,P0、P1、P2、P3为计数器输入端,MR为清除端,Q0、Q1、Q2、Q3为数据输出端。

其功能表如下:

|

输入

|

输出

|

|

MR

|

PLU

|

CPU

|

CPD

|

P3

|

P2

|

P1

|

P0

|

Q3

|

Q2

|

Q1

|

Q0

|

|

1

|

×

|

×

|

×

|

×

|

×

|

×

|

×

|

0

|

0

|

0

|

0

|

|

0

|

0

|

×

|

×

|

d

|

c

|

b

|

a

|

d

|

c

|

b

|

a

|

|

0

|

1

|

|

1

|

×

|

×

|

×

|

×

|

加计数

|

|

0

|

1

|

1

|

|

×

|

×

|

×

|

×

|

减计数

|

表2 74LS192的功能表

测试74LS90的逻辑功能

计数脉冲由单次脉冲源提供,如果从A端输入,从QA端输出,则是二进制计数器;如果从B端输入,从QD,QC,QB输出。则是异步五进制加法计数器;当QA和B端相连,时钟脉冲从A端输入,从QD,QC,QB,QA端输出,则是8421码十进制计数器;当A端和QD端相连,时钟脉冲从B端输入,从QD,QC,QB,QA端输出,则是5421码十进制计数器。输出端QD、QC、QB、QA接一译码器74LS248(或74LS48),经过译码后接至数码管单元的共阴数码管。按表1逐项测试并判断该集成块的功能是否正常。具体的接法请参考附录和有关资料。

3、测试74LS192(或CC40192)的逻辑功能

计数脉冲由单次脉冲源提供,清除端、置数端、数据输入端P3、P2、P1、P0分别接至逻辑电平输出插孔,输出端Q3、Q2、Q1、Q0接一译码器74LS248(或74LS48),经过译码后接至数码管单元的共阴数码,非同步进位输出端与非同步借位输出端接逻辑电平显示插孔。按表2逐项测试并判断该集成块的功能是否正常。具体的接法请参考附录和有关资料。

4、测试74LS161的逻辑功能

具体的测试方法同实验内容2,3,只是74LS161的管脚分布不同,功能不同。同样需要将74LS161的输出经过译码后在数码管上显示出来,关于74LS161的功能及用法,74LS248的功能及用法请参考有关资料。

5、 如图6所示,用两片74LS192组成二位十进制加法计数器,输入1Hz的连续脉冲,进行由00到99的累加计数,并记录之。同样可以将74LS192的输出端接译码器,用二个数码管来显示其计数情况。

6、将二位十进制加法计数器改为二位十进制减法计数器,实现由99到00的递减计数,并记录之。具体的实现方法请自己查阅有关资料,画出详细的接线图,在扩展板上实现。

苏州博泰伟业电子科技有限公司是同行业中最实惠的,是客户口中“质量第一,信誉第一”的提供苏州电子天平,超市打印条码秤收银秤,电子台秤维修,电子台秤报价,电子汽车衡,电子吊秤,电子地磅,电子秤维修,欢迎新老顾客前来咨询。地址:苏州市高新区滨河路625号创业大厦2号楼2楼

|